# INTEGRATED CIRCUITS

Preliminary specification Supersedes data of 1999 Jun 15 IC28 Data Handbook 2000 Apr 03

### **GENERAL DESCRIPTION**

The XA-G49 is a member of Philips' 80C51 XA (eXtended Architecture) family of high performance 16-bit single-chip microcontrollers.

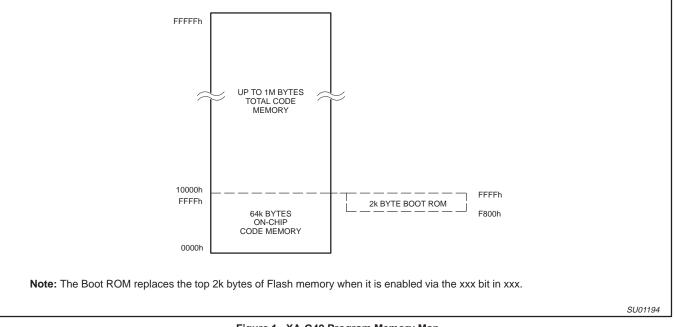

The XA-G49 contains 64k bytes of Flash program memory, and provides three general purpose timers/counters, a watchdog timer, dual UARTs, and four general purpose I/O ports with programmable output configurations.

A default serial loader program in the Boot ROM allows In-System Programming (ISP) of the Flash memory without the need for a loader in the Flash code. User programs may erase and reprogram the Flash memory at will through the use of standard routines contained in the Boot ROM (In-Application Programming).

### FEATURES

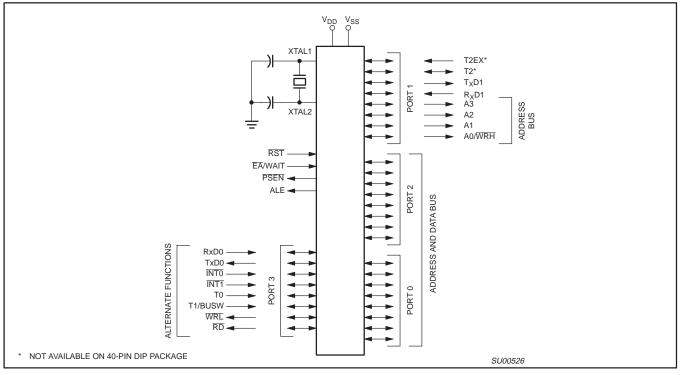

**BLOCK DIAGRAM**

- 4.5V to 5.5V operation. For low voltage operation, consult factory.

- 64K bytes of on-chip Flash program memory with In-System Programming capability

- Five Flash blocks = two 8k byte blocks and three 16k byte blocks

- Nearly identical to XA-G3, except for double the program and RAM memories

- Single supply voltage In-System Programming (ISP) of the Flash memory (V<sub>PP</sub> = V<sub>DD</sub>, or V<sub>PP</sub> = 12V if desired)

- Boot ROM contains low level Flash programming routines for In-Application Programming and a default serial loader using the UART

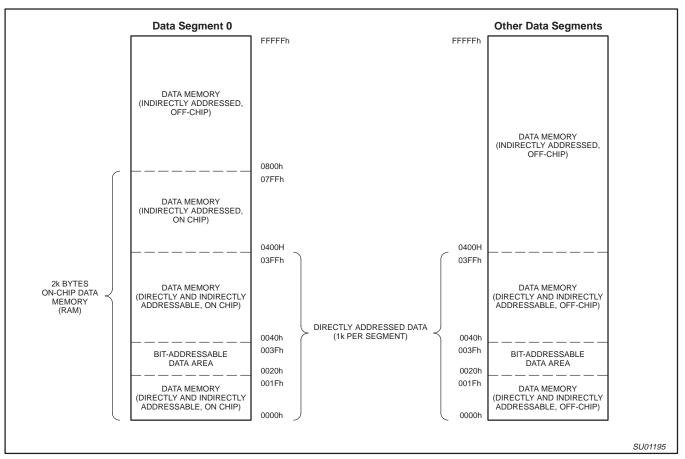

- 2048 bytes of on-chip data RAM

- Supports off-chip program and data addressing up to 1 megabyte (20 address lines)

- Three standard counter/timers with enhanced features (same as XA-G3 T0, T1, and T2). All timers have a toggle output capability

- Watchdog timer

- Two enhanced UARTs with independent baud rates

- Seven software interrupts

- Four 8-bit I/O ports, with 4 programmable output configurations for each pin

- 30 MHz operating frequency at 5V

- Power saving operating modes: Idle and Power-Down. Wake-Up from power-down via an external interrupt is supported.

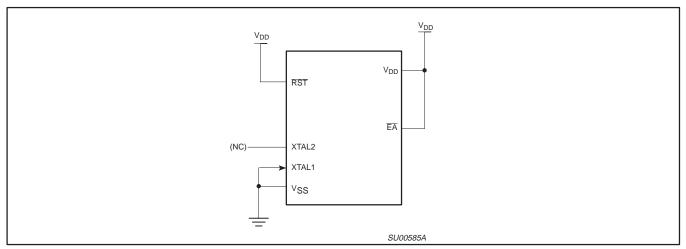

- 44-pin PLCC and 44-pin LQFP packages

### **XA CPU Core** Program SFR Memory bus Bus UART 0 64K Bytes FLAŚH Data Bus UART 1 2048 Bytes Static RAM Timer 0, 1 Port 0 Port 1 Timer 2 Port 2 Watchdog Port 3 Timer SU01002

### 2000 Apr 03

XA-G49

### ORDERING INFORMATION

| FLASH     | TEMPERATURE RANGE (°C)<br>AND PACKAGE            | FREQ.<br>(MHz) | DRAWING<br>NUMBER |

|-----------|--------------------------------------------------|----------------|-------------------|

| PXAG49KBA | 0 to +70<br>44-pin Plastic Leaded Chip Carrier   | 30             | SOT187-2          |

| PXAG49KFA | –40 to +85<br>44-pin Plastic Leaded Chip Carrier | 30             | SOT187-2          |

### LOGIC SYMBOL

**XA-G49**

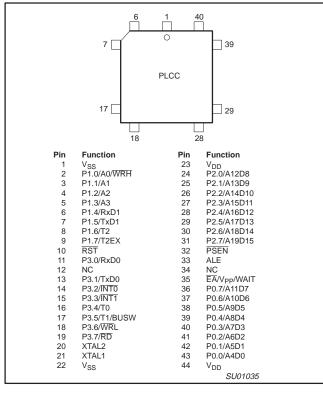

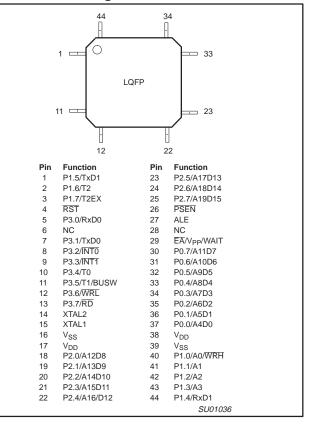

### PIN CONFIGURATIONS

### 44-Pin PLCC Package

### 44-Pin LQFP Package

### **PIN DESCRIPTIONS**

|                 | PIN. NO.     |               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------|--------------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MNEMONIC        | LCC          | LQFP          | TYPE  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| $V_{SS}$        | 1, 22        | 16            | I     | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | е.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| V <sub>DD</sub> | 23, 44       | 17            | I     | Power Supply: This i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | is the power supply voltage for normal, idle, and power down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| P0.0 – P0.7     | 43–36        | 37–30         | I/O   | written to them and an<br>port 0 pins as inputs a<br>configured independe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. Port 0 latches have 1s vritten to them and are configured in the quasi-bidirectional mode during reset. The operation of ort 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is onfigured independently. Refer to the section on I/O port configuration and the DC Electrical characteristics for details.                                                                                          |  |  |  |  |

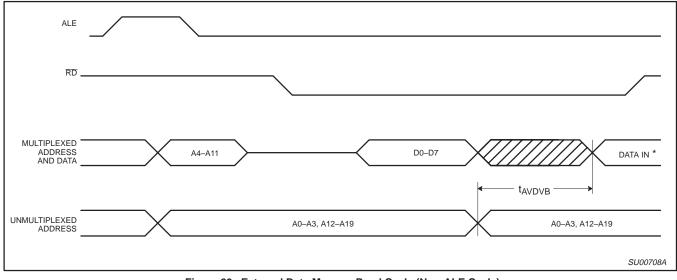

|                 |              |               |       | When the external pro<br>byte and address line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ogram/data bus is used, Port 0 becomes the multiplexed low data/instruction s 4 through 11.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| P1.0 – P1.7     | 2–9          | 40–44,<br>1–3 | I/O   | written to them and an<br>port 1 pins as inputs a<br>configured independe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Port 1:</b> Port 1 is an 8-bit I/O port with a user-configurable output type. Port 1 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of port 1 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.                                                                                        |  |  |  |  |

|                 |              |               |       | Port 1 also provides s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | pecial functions as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                 | 2            | 40            | 0     | C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Address bit 0 of the external address bus when the external data bus is<br>onfigured for an 8 bit width. When the external data bus is configured for a 16<br>it width, this pin becomes the high byte write strobe.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                 | 3            | 41            | 0     | <b>A1:</b> A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ddress bit 1 of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                 | 4            | 42            | 0     | A2: A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ddress bit 2 of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                 | 5            | 43            | 0     | <b>A3:</b> A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ddress bit 3 of the external address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                 | 6            | 44            | I I . | RxD1 (P1.4): F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Receiver input for serial port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                 | 7            | 1             | 0     | TxD1 (P1.5): ⊺                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ransmitter output for serial port 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                 | 8            | 2             | I/O   | T2 (P1.6): ⊺                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ïmer/counter 2 external count input/clockout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                 | 9            | 3             | 1     | T2EX (P1.7): T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | imer/counter 2 reload/capture/direction control                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

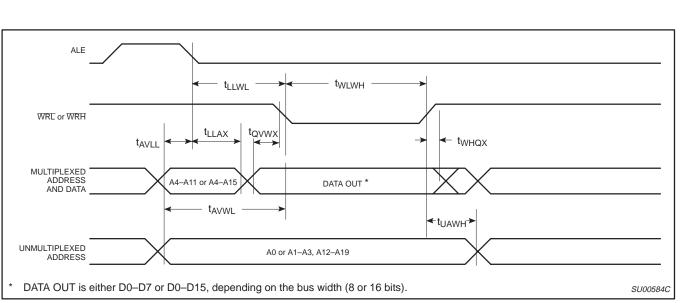

| P2.0 – P2.7     | 24–31        | 18–25         | I/O   | <b>Port 2:</b> Port 2 is an 8-bit I/O port with a user-configurable output type. Port 2 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of port 2 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details. When the external program/data bus is used in 16-bit mode, Port 2 becomes the multiplexed high data/instruction byte and address lines 12 through 19. When the external program/data bus is used in 6-bit mode, Port 2 becomes the multiplexed high data/instruction byte and address lines 12 through 19. When the external program/data bus is used in |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| P3.0 – P3.7     | 11,<br>13–19 | 5,<br>7–13    | I/O   | <b>Port 3:</b> Port 3 is an 8-<br>written to them and an<br>port 3 pins as inputs a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-bit mode, the number of address lines that appear on port 2 is user programmable.<br><b>Port 3:</b> Port 3 is an 8-bit I/O port with a user configurable output type. Port 3 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. the operation of port 3 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details. |  |  |  |  |

|                 |              |               |       | Port 3 also provides v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rarious special functions as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                 | 11           | 5             | 1     | RxD0 (P3.0):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Receiver input for serial port 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                 | 13           | 7             | 0     | TxD0 (P3.1):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transmitter output for serial port 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                 | 14           | 8             |       | INT0 (P3.2):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | External interrupt 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                 | 15           | 9             | 1     | INT1 (P3.3):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | External interrupt 1 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                 | 16           | 10            | I/O   | T0 (P3.4):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Timer 0 external input, or timer 0 overflow output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                 | 17           | 11            | I/O   | T1/BUSW (P3.5):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Timer 1 external input, or timer 1 overflow output. The value on this pin is latched as the external reset input is released and defines the default external data bus width (BUSW). $0 = 8$ -bit bus and $1 = 16$ -bit bus.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                 | 18           | 12            | 0     | WRL (P3.6):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | External data memory low byte write strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                 | 19           | 13            | 0     | RD (P3.7):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | External data memory read strobe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

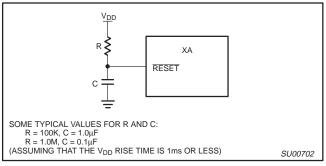

| RST             | 10           | 4             | I     | their default states, an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | oin resets the microcontroller, causing I/O ports and peripherals to take on<br>nd the processor to begin execution at the address contained in the reset<br>ection on Reset for details.                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

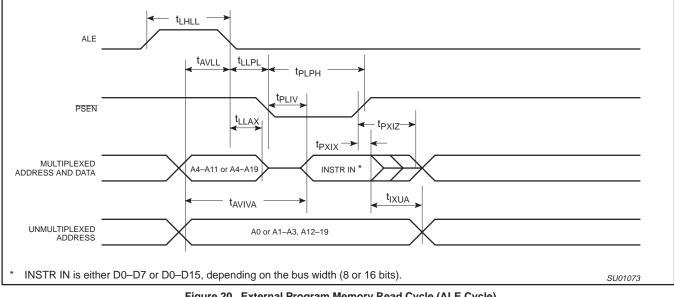

| ALE             | 33           | 27            | I/O   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>Ie:</b> A high output on the ALE pin signals external circuitry to latch the address xed address/data bus. A pulse on ALE occurs only when it is needed in order e.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

XA-G49

| MNEMONIC                    | PIN. | NO.  | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | LCC  | LQFP |      | NAME AND FONCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PSEN                        | 32   | 26   | 0    | <b>Program Store Enable:</b> The read strobe for external program memory. When the microcontroller accesses external program memory, <u>PSEN</u> is driven low in order to enable memory devices. <u>PSEN</u> is only active when external code accesses are performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

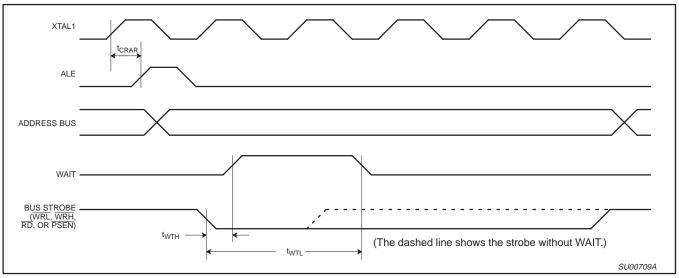

| EA/WAIT/<br>V <sub>PP</sub> | 35   | 29   | I    | <b>External Access/Wait/Programming Supply Voltage:</b> The EA input determines whether the internal program memory of the microcontroller is used for code execution. The value on the EA pin is latched as the external reset input is released and applies during later execution. When latched as a 0, external program memory is used exclusively, when latched as a 1, internal program memory will be used up to its limit, and external program memory used above that point. After reset is released, this pin takes on the function of bus Wait input. If Wait is asserted high during any external bus access, that cycle will be extended until Wait is released. During EPROM programming, this pin is also the programming supply voltage input. |

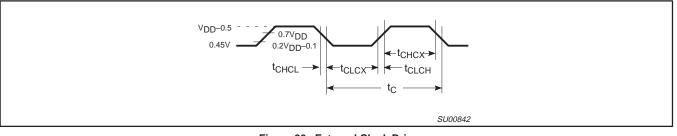

| XTAL1                       | 21   | 15   | I    | <b>Crystal 1:</b> Input to the inverting amplifier used in the oscillator circuit and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTAL2                       | 20   | 14   | 0    | Crystal 2: Output from the oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### SPECIAL FUNCTION REGISTERS

| NAME | DESCRIPTION                   | SFR<br>ADDRESS | MSB    |        | BIT FUNC | TIONS A | ND ADDI | RESSES |      | LSB  | RESET<br>VALUE |

|------|-------------------------------|----------------|--------|--------|----------|---------|---------|--------|------|------|----------------|

|      |                               |                |        |        |          | i       |         |        |      |      |                |

| AUXR | Auxiliary function register   | 44C            | ENBOOT | FMIDLE | PWR_VLD  | _       | _       | —      | _    |      |                |

| BCR  | Bus configuration register    | 46A            | —      | —      | —        | WAITD   | BUSD    | BC2    | BC1  | BC0  | Note 1         |

| BTRH | Bus timing register high byte | 469            | DW1    | DW0    | DWA1     | DWA0    | DR1     | DR0    | DRA1 | DRA0 | FF             |

| BTRL | Bus timing register low byte  | 468            | WM1    | WM0    | ALEW     | —       | CR1     | CR0    | CRA1 | CRA0 | EF             |

| CS   | Code segment                  | 443            |        |        |          |         |         |        |      |      | 00             |

| DS   | Data segment                  | 441            |        |        |          |         |         |        |      |      | 00             |

| ES   | Extra segment                 | 442            | 33F    | 33E    | 33D      | 33C     | 33B     | 33A    | 339  | 338  | 00             |

| IEH* | Interrupt enable high byte    | 427            | _      | _      | —        | _       | ETI1    | ERI1   | ETI0 | ERI0 | 00             |

|      |                               |                | 337    | 336    | 335      | 334     | 333     | 332    | 331  | 330  | 1              |

| IEL* | Interrupt enable low byte     | 426            | EA     | —      | —        | ET2     | ET1     | EX1    | ET0  | EX0  | 00             |

| IPA0 | Interrupt priority 0          | 4A0            |        |        | PT0      |         | _       |        | PX0  |      | 00             |

| IPA1 | Interrupt priority 1          | 4A1            |        |        | PT1      |         | _       |        | PX1  |      | 00             |

| IPA2 | Interrupt priority 2          | 4A2            | _      |        | _        |         |         |        | PT2  |      | 00             |

| IPA4 | Interrupt priority 4          | 4A4            | _      |        | PTI0     |         | —       |        | PRI0 |      | 00             |

| IPA5 | Interrupt priority 5          | 4A5            | _      |        | PTI1     |         | _       |        | PRI1 |      | 00             |

|      |                               |                | 387    | 386    | 385      | 384     | 383     | 382    | 381  | 380  | ]              |

| P0*  | Port 0                        | 430            | AD7    | AD6    | AD5      | AD4     | AD3     | AD2    | AD1  | AD0  | FF             |

|      |                               |                | 38F    | 38E    | 38D      | 38C     | 38B     | 38A    | 389  | 388  |                |

| P1*  | Port 1                        | 431            | T2EX   | T2     | TxD1     | RxD1    | A3      | A2     | A1   | WRH  | FF             |

|      |                               |                | 397    | 396    | 395      | 394     | 393     | 392    | 391  | 390  | ]              |

| P2*  | Port 2                        | 432            | P2.7   | P2.6   | P2.5     | P2.4    | P2.3    | P2.2   | P2.1 | P2.0 | FF             |

|      |                               |                | 39F    | 39E    | 39D      | 39C     | 39B     | 39A    | 399  | 398  |                |

| P3*  | Port 3                        | 433            | RD     | WR     | T1       | Т0      | INT1    | INT0   | TxD0 | RxD0 | FF             |

|      |                               |                |        |        |          |         |         |        |      |      |                |

### Preliminary specification

# XA 16-bit microcontroller family 64K Flash/2K RAM, watchdog, 2 UARTs

| NAME             | DESCRIPTION                                                                | SFR<br>ADDRESS | MSB   |       | BIT FUN | CTIONS A | ND ADD | RESSES |       | LSB          | RESET<br>VALUE |

|------------------|----------------------------------------------------------------------------|----------------|-------|-------|---------|----------|--------|--------|-------|--------------|----------------|

| P0CFGA           | Port 0 configuration A                                                     | 470            |       |       |         |          |        |        |       |              | Note 5         |

| P1CFGA           | Port 1 configuration A                                                     | 471            |       |       |         |          |        |        |       |              | Note 5         |

| P2CFGA           | Port 2 configuration A                                                     | 472            |       |       |         |          |        |        |       |              | Note 5         |

| P3CFGA           | Port 3 configuration A                                                     | 473            |       |       |         |          |        |        |       |              | Note 5         |

| P0CFGB           | Port 0 configuration B                                                     | 4F0            |       |       |         |          |        |        |       |              | Note 5         |

| P1CFGB           | Port 1 configuration B                                                     | 4F1            |       |       |         |          |        |        |       |              | Note 5         |

| P2CFGB           | Port 2 configuration B                                                     | 4F2            |       |       |         |          |        |        |       |              | Note 5         |

| P3CFGB           | Port 3 configuration B                                                     | 4F3            |       |       |         |          |        |        |       |              | Note 5         |

|                  |                                                                            |                | 227   | 226   | 225     | 224      | 223    | 222    | 221   | 220          |                |

| PCON*            | Power control register                                                     | 404            | —     | —     | —       | —        | _      | —      | PD    | IDL          | 00             |

|                  |                                                                            |                | 20F   | 20E   | 20D     | 20C      | 20B    | 20A    | 209   | 208          | 1              |

| PSWH*            | Program status word<br>(high byte)                                         | 401            | SM    | ТМ    | RS1     | RS0      | IM3    | IM2    | IM1   | IM0          | Note 2         |

|                  |                                                                            |                | 207   | 206   | 205     | 204      | 203    | 202    | 201   | 200          | 1              |

| PSWL*            | Program status word (low byte)                                             | 400            | С     | AC    | _       | _        | _      | V      | N     | Z            | Note 2         |

|                  |                                                                            |                | 217   | 216   | 215     | 214      | 213    | 212    | 211   | 210          | 1              |

| PSW51*           | 80C51 compatible PSW                                                       | 402            | С     | AC    | F0      | RS1      | RS0    | V      | F1    | Р            | Note 3         |

| RTH0             | Timer 0 extended reload,<br>high byte                                      | 455            |       |       |         |          |        |        |       |              | 00             |

| RTH1             | Timer 1 extended reload, high byte                                         | 457            |       |       |         |          |        |        |       |              | 00             |

| RTL0             | Timer 0 extended reload,<br>low byte                                       | 454            |       |       |         |          |        |        |       |              | 00             |

| RTL1             | Timer 1 extended reload,<br>low byte                                       | 456            | 307   | 306   | 305     | 304      | 303    | 302    | 301   | 300          | 00             |

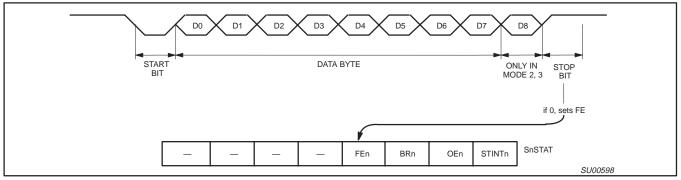

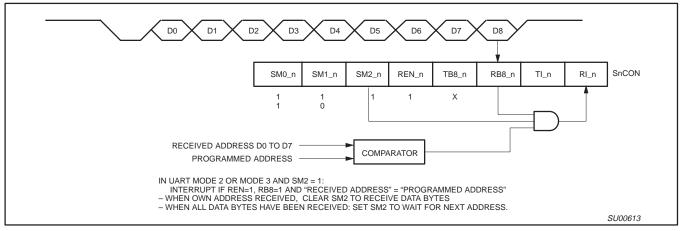

| S0CON*           | Serial port 0 control register                                             | 420            | SM0 0 | SM1_0 | SM2_0   | REN_0    | TB8_0  | RB8_0  | TI_0  | RI_0         | 00             |

| 30001            | Serial port o control register                                             | 420            | 30F   | 30E   | 30D     | 30C      | 30B    | 30A    | 309   | 308          | 00             |

| S0STAT*          | Serial port 0 extended status                                              | 421            |       | 30E   | 30D     | 300      | FE0    | BR0    | OE0   | STINT0       | 00             |

| SOBUE            | Serial port 0 buffer register                                              | 421            |       | _     |         |          | FLU    | BRU    | OLU   | 311110       |                |

| SOADDR           | Serial port 0 address register                                             | 460            |       |       |         |          |        |        |       |              | x<br>00        |

| SOADEN           | Serial port 0 address enable register                                      | 462            |       |       |         |          |        |        |       |              | 00             |

|                  |                                                                            |                | 327   | 326   | 325     | 324      | 323    | 322    | 321   | 320          |                |

| S1CON*           | Serial port 1 control register                                             | 424            | SM0_1 | SM1_1 | SM2_1   | REN_1    | TB8_1  | RB8_1  | TI_1  | RI_1         | 00             |

|                  |                                                                            |                | 32F   | 32E   | 32D     | 32C      | 32B    | 32A    | 329   | 328          |                |

| S1STAT*          | Serial port 1 extended status                                              | 425            | _     | —     | —       | -        | FE1    | BR1    | OE1   | STINT1       | 00             |

| S1BUF            | Serial port 1 buffer register                                              | 464            |       |       |         |          |        |        |       |              | x              |

| S1ADDR<br>S1ADEN | Serial port 1 address register<br>Serial port 1 address enable<br>register | 465<br>466     |       |       |         |          |        |        |       |              | 00<br>00       |

| SCR              | System configuration register                                              | 440            | _     | _     | _       | _        | PT1    | PT0    | СМ    | PZ           | 00             |

|                  |                                                                            |                | 21F   | 21E   | 21D     | 21C      | 21B    | 21A    | 219   | 218          | 1              |

| SSEL*            | Segment selection register                                                 | 403            | ESWEN | R6SEG | R5SEG   | R4SEG    | R3SEG  | R2SEG  | R1SEG | <b>R0SEG</b> | 00             |

| SWE              | Software Interrupt Enable                                                  | 47A            | _     | SWE7  | SWE6    | SWE5     | SWE4   | SWE3   | SWE2  | SWE1         | 00             |

|        | DECODIDEION                           | SFR     |      |      | BIT FUNC |       |       | RESSES |       |        | RESET  |

|--------|---------------------------------------|---------|------|------|----------|-------|-------|--------|-------|--------|--------|

| NAME   | DESCRIPTION                           | ADDRESS | MSB  |      |          |       |       |        |       | LSB    | VALUE  |

|        |                                       |         | 357  | 356  | 355      | 354   | 353   | 352    | 351   | 350    |        |

| SWR*   | Software Interrupt Request            | 42A     | _    | SWR7 | SWR6     | SWR5  | SWR4  | SWR3   | SWR2  | SWR1   | 00     |

|        |                                       |         | 2C7  | 2C6  | 2C5      | 2C4   | 2C3   | 2C2    | 2C1   | 2C0    | 1      |

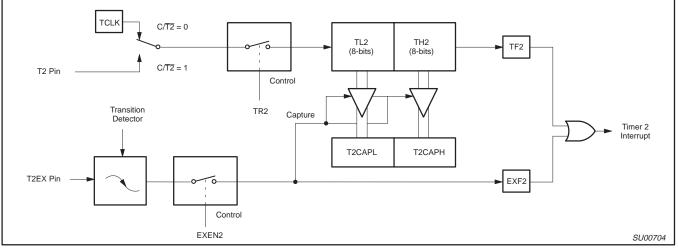

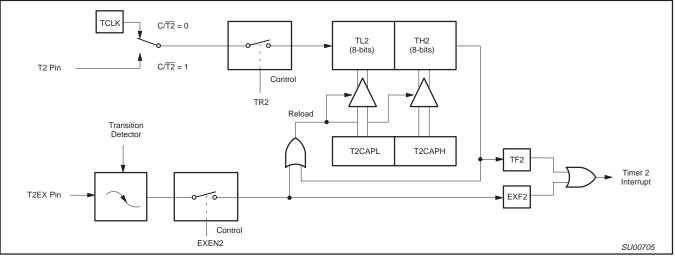

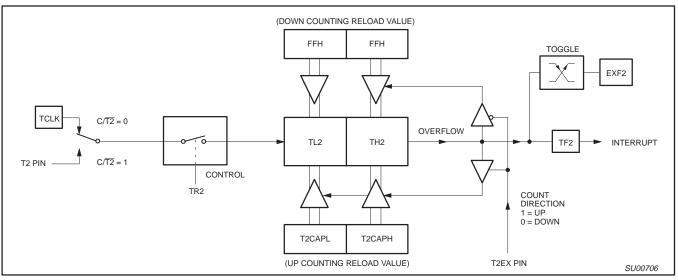

| T2CON* | Timer 2 control register              | 418     | TF2  | EXF2 | RCLK0    | TCLK0 | EXEN2 | TR2    | C/T2  | CP/RL2 | 00     |

|        |                                       |         | 2CF  | 2CE  | 2CD      | 2CC   | 2CB   | 2CA    | 2C9   | 2C8    | 1      |

| T2MOD* | Timer 2 mode control                  | 419     | _    | —    | RCLK1    | TCLK1 | —     | _      | T2OE  | DCEN   | 00     |

| TH2    | Timer 2 high byte                     | 459     |      |      |          |       |       |        |       |        | 00     |

| TL2    | Timer 2 low byte                      | 458     |      |      |          |       |       |        |       |        | 00     |

| T2CAPH | Timer 2 capture register, high byte   | 45B     |      |      |          |       |       |        |       |        | 00     |

| T2CAPL | Timer 2 capture register,<br>low byte | 45A     |      |      |          |       |       |        |       |        | 00     |

|        |                                       |         | 287  | 286  | 285      | 284   | 283   | 282    | 281   | 280    |        |

| TCON*  | Timer 0 and 1 control register        | 410     | TF1  | TR1  | TF0      | TR0   | IE1   | IT1    | IE0   | IT0    | 00     |

| TH0    | Timer 0 high byte                     | 451     |      |      |          |       |       |        |       |        | 00     |

| TH1    | Timer 1 high byte                     | 453     |      |      |          |       |       |        |       |        | 00     |

| TL0    | Timer 0 low byte                      | 450     |      |      |          |       |       |        |       |        | 00     |

| TL1    | Timer 1 low byte                      | 452     |      |      |          |       |       |        |       |        | 00     |

| TMOD   | Timer 0 and 1 mode control            | 45C     | GATE | C/T  | M1       | MO    | GATE  | C/T    | M1    | MO     | 00     |

|        |                                       |         | 28F  | 28E  | 28D      | 28C   | 28B   | 28A    | 289   | 288    | ]      |

| TSTAT* | Timer 0 and 1 extended status         | 411     | _    | —    | —        | —     | _     | T1OE   | —     | T0OE   | 00     |

|        |                                       |         | 2FF  | 2FE  | 2FD      | 2FC   | 2FB   | 2FA    | 2F9   | 2F8    | 1      |

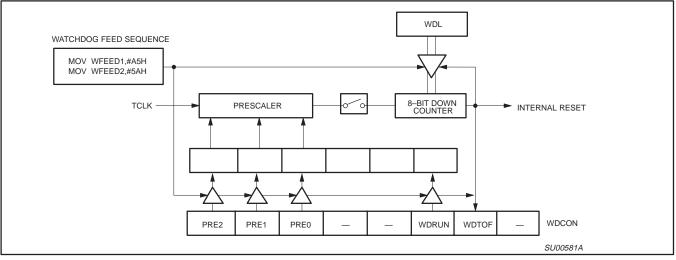

| WDCON* | Watchdog control register             | 41F     | PRE2 | PRE1 | PRE0     | - 1   | —     | WDRUN  | WDTOF | _      | Note 6 |

| WDL    | Watchdog timer reload                 | 45F     |      |      | •        |       |       |        |       | •      | 00     |

| WFEED1 | Watchdog feed 1                       | 45D     |      |      |          |       |       |        |       |        | x      |

| WFEED2 | Watchdog feed 2                       | 45E     |      |      |          |       |       |        |       |        | x      |

#### NOTES:

SFRs are bit addressable.

1. At reset, the BCR register is loaded with the binary value 0000 0a11, where "a" is the value on the BUSW pin. This defaults the address bus size to 20 bits since the XA-G49 has only 20 address lines.

2. SFR is loaded from the reset vector.

3. All bits except F1, F0, and P are loaded from the reset vector. Those bits are all 0.

Unimplemented bits in SFRs are X (unknown) at all times. Ones should not be written to these bits since they may be used for other purposes in future XA derivatives. The reset value shown for these bits is 0.

Port configurations default to quasi-bidirectional when the XA begins execution from internal code memory after reset, based on the

5. Port configurations default to quasi-bidirectional when the XA begins execution from internal code memory after reset, based on the condition found on the EA pin. Thus all PnCFGA registers will contain FF and PnCFGB registers will contain 00. When the XA begins execution using external code memory, the default configuration for pins that are associated with the external bus will be push-pull. The PnCFGA and PnCFGB register contents will reflect this difference.

6. The WDCON reset value is E6 for a Watchdog reset, E4 for all other reset causes.

7. The XA-G49 implements an 8-bit SFR bus, as stated in Chapter 8 of the XA User Guide. All SFR accesses must be 8-bit operations. Attempts to write 16 bits to an SFR will actually write only the lower 8 bits. Sixteen bit SFR reads will return undefined data in the upper byte.

The AUXR reset value is typically 00h. If the Boot Loader is activated at reset because the Flash status byte is non-zero or because the Boot Vector has been forced (by PSEN = 0, ALE = 1, EA = 1 at reset), the AUXR reset value will be 1x00 0000b. Bit 6 will be a 1 if the on-chip V<sub>PP</sub> generator is running and ready, otherwise it will be a 0.

Figure 1. XA-G49 Program Memory Map

Figure 2. XA-G49 Data Memory Map

**XA-G49**

# XA 16-bit microcontroller family 64K Flash/2K RAM, watchdog, 2 UARTs

### FLASH EPROM MEMORY

#### **GENERAL DESCRIPTION**

The XA-G49 Flash memory augments EPROM functionality with in-circuit electrical erasure and programming. The Flash can be read and written as bytes. The Chip Erase operation will erase the entire program memory. The Block Erase function can erase any single Flash block. In-circuit programming and standard parallel programming are both available. On-chip erase and write timing generation contribute to a user friendly programming interface.

The XA-G49 Flash reliably stores memory contents even after 10,000 erase and program cycles. The cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and programming operations produces reliable cycling. For In-System Programming, the XA-G49 can use a single +5 V power supply. Faster In-System Programming may be obtained, if required, through the use of a +12 V V<sub>PP</sub> supply. Parallel programming (using separate programming hardware) uses a +12 V V<sub>PP</sub> supply.

### FEATURES

- Flash EPROM internal program memory with Single Voltage Programming and Block Erase capability.

- Internal 2k byte fixed boot ROM, containing low-level programming routines and a default loader. The Boot ROM can be turned off to provide access to the full 64k byte Flash memory.

- Boot vector allows user provided Flash loader code to reside anywhere in the Flash memory space. This configuration provides flexibility to the user.

- Default loader in Boot ROM allows programming via the serial port without the need for a user provided loader.

- Up to 1 Mbyte external program memory if the internal program memory is disabled (EA = 0).

- Programming and erase voltage: V<sub>PP</sub> = V<sub>DD</sub> (single 5V ±5% chip power supply), or 12V ±5% for In System Programming. Using 12V V<sub>PP</sub> for ISP may improve programming and erase time.

- Read/Programming/Erase:

- Byte-wise read (60 ns access time at 4.5 V).

- Byte Programming (40 μs).

- Typical erase times:

Block Erase (8k bytes or 16k bytes) in t.b.d. seconds.

Full Erase (64k bytes) in t.b.d. seconds.

- In-circuit programming via user selected method, typically RS232 or parallel I/O port interface.

- Programmable security for the code in the Flash

- 1,000 minimum erase/program cycles each byte over operating temperature range

- 10 year minimum data retention.

### CAPABILITIES OF THE PHILIPS 89C51 FLASH-BASED MICROCONTROLLERS

#### Flash organization

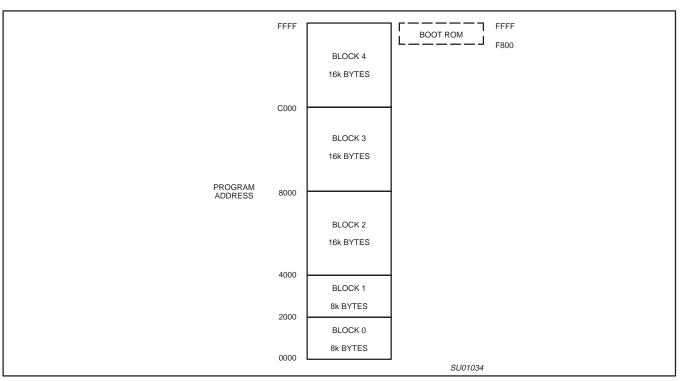

The XA-G49 contains 64k bytes of Flash program memory. This memory is organized as 5 separate blocks. The first two blocks are 8k bytes in size, filling the program memory space from address 0 through 3FFF hex. The final three blocks are 16k bytes in size and occupy addresses from 4000 through FFFF hex.

Figure 3 depicts the Flash memory configuration.

#### Flash Programming and Erasure

The XA-G49 Flash microcontroller supports a number of programming possibilities for the on-chip Flash memory. The Flash memory may be programmed in a parallel fashion on standard programming equipment in a manner similar to an EPROM microcontroller. The XA-G49 microcontroller is able to program its own Flash memory while the application code is running. Also, a default loader built into a Boot ROM allows programming blank devices serially through the UART.

Using any of these types of programming, any of the individual blocks may be erased separately, or the entire chip may be erased. Programming of the Flash memory is accomplished one byte at a time.

#### Boot ROM

When the microcontroller programs its own Flash memory, all of the low level details are handled by code that is permanently contained in a 2k byte "Boot ROM" that is separate from the Flash memory. A user program simply calls the entry point with the appropriate parameters to accomplish the desired operation. Boot ROM operations include things like: erase block, program byte, verify byte, program security lock bit, etc. The Boot ROM overlays the program memory space at the top of the address space from F800 to FFFF hex, when it is enabled by setting the ENBOOT bit at AUXR1.7.. The Boot ROM may be turned off so that the upper 2k bytes of Flash program memory are accessible for execution.

#### ENBOOT and PWR\_VLD

Setting the ENBOOT bit in the AUXR register enables the Boot ROM and activates the on-chip V<sub>PP</sub> generator if V<sub>PP</sub> is connected to V<sub>DD</sub> rather than 12V externally. The PWR\_VLD flag indicates that V<sub>PP</sub> is available for programming and erase operations. This flag should be checked prior to calling the Boot ROM for programming and erase services. When ENBOOT is set, it typically takes 5 microseconds for the internal programming voltage to be ready.

The ENBOOT bit will automatically be set if the status byte is non-zero during reset, or when  $\overrightarrow{\text{PSEN}}$  is low, ALE is high, and  $\overrightarrow{\text{EA}}$  is high at the falling edge of reset. Otherwise, ENBOOT will be cleared during reset.

When programming functions are not needed, ENBOOT may be cleared. This enables access to the 2k bytes of Flash code memory that is overlaid by the Boot ROM, allowing a full 64k bytes of Flash code memory.

Figure 3. Flash Memory Configuration

### FMIDLE

The FMIDLE bit in the AUXR register allows saving additional power by turning off the Flash memory when the CPU is in the Idle mode. This must be done just prior to initiating the Idle mode, as shown below.

| OR | AUXR,#\$40 | ; Set Flash memory   |

|----|------------|----------------------|

|    |            | to idle mode.        |

| OR | PCON,#\$01 | ; Turn on Idle mode. |

|    | •          | ; Execution resumes  |

|    |            | here when Idle       |

|    |            | mode terminates.     |

When the Flash memory is put into the Idle mode by setting FMIDLE, restarting the CPU upon exiting Idle mode takes slightly longer, about 3 microseconds. However, the standby current consumed by the Flash memory is reduced from about 8mA to about 1mA.

#### **Default Loader**

A default loader that accepts programming commands in a predetermined format is contained permanently in the Boot ROM. A factory fresh device will enter this loader automatically if it is powered up without first being programmed by the user. Loader commands include functions such as erase block; program Flash memory; read Flash memory; and blank check.

#### **Boot Vector**

The XA-G49 contains two special FLASH registers: the BOOT VECTOR and the STATUS BYTE.

The "Boot Vector" allows forcing the execution of a user supplied Flash loader upon reset, under two specific sets of conditions. At the falling edge of reset, the XA-G49 examines the contents of the Status Byte. If the Status Byte is set to zero, power-up execution starts at location 0000H, which is the normal start address of the user's application code. When the Status Byte is set to a value other than zero, the Boot Vector is used as the reset vector (4 bytes), including the Boot Program Counter (BPC) and the Boot PSW (BPSW). The factory default settings are 8000h for the BPSW and F800h for the BPC, which corresponds to the address F900h for the factory masked-ROM ISP boot loader. The Status Byte is automatically set to a non-zero value when a programming error occurs. A custom boot loader can be written with the Boot Vector set to the custom boot loader.

**NOTE:** When erasing the Status Byte or Boot Vector, these bytes are erased at the same time. It is necessary to reprogram the Boot Vector after erasing and updating the Status Byte.

### Hardware Activation of the Boot Vector

Program execution at the Boot Vector may also be forced from outside of the microcontroller by setting the correct state on a few pins. While Reset is asserted, the PSEN pin must be pulled low, the ALE pin allowed to float high (need not be pulled up externally), and the EA pin driven to a logic high (or up to  $V_{PP}$ ). Then reset may be released. This is the same effect as having a non-zero status byte. This allows building an application that will normally execute the end user's code but can be manually forced into ISP operation. The Boot ROM is enabled when use of the Boot Vector is forced as described above, so the branch may go to the default loader. Conversely, user code in the top 2k bytes of the Flash memory may not be executed when the Boot Vector is used.

If the factory default setting for the BPC (F800h) is changed, it will no longer point to the ISP masked-ROM boot loader code. If this happens, the only possible way to change the contents of the Boot Vector is through the parallel programming method, provided that the end user application does not contain a customized loader that provides for erasing and reprogramming of the Boot Vector and Status Byte.

After programming the FLASH, the status byte should be erased to zero in order to allow execution of the user's application code beginning at address 0000H.

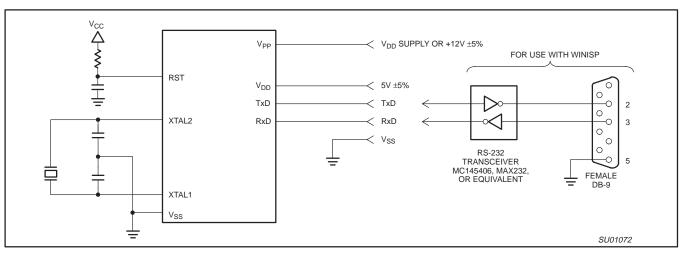

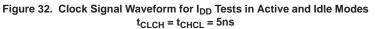

Figure 4. In-System Programming with a Minimum of Pins

#### In-System Programming (ISP)

In-System Programming (ISP) is performed without removing the microcontroller from the system. The In-System Programming (ISP) facility consists of a series of internal hardware resources coupled with internal firmware to facilitate remote programming of the XA-G49 through the serial port. This firmware is provided by Philips and embedded within each XA-G49 device.

The Philips In-System Programming (ISP) facility has made in-circuit programming in an embedded application possible with a minimum of additional expense in components and circuit board area.

The ISP function uses five pins: TxD, RxD, V<sub>SS</sub>, V<sub>DD</sub>, and V<sub>PP</sub> (see Figure 4). Only a small connector needs to be available to interface your application to an external circuit in order to use this feature. The V<sub>PP</sub> supply should be adequately decoupled and V<sub>PP</sub> not allowed to exceed datasheet limits.

#### Table 1. ISP typical programming currents @ 25°C, 22 MHz, 5 V<sub>DD</sub>

| V <sub>CC</sub> | V <sub>PP</sub> | I <sub>PP</sub> | I <sub>DD</sub> |

|-----------------|-----------------|-----------------|-----------------|

| 5.0 V           | 5.0 V           | 60 µA           | 25 mA           |

ISP increases I<sub>DD</sub> by less than 1mA.

#### ISP software is available on the Philips web site

- 1. With your browser, open this page: www.semiconductors.com

- 2. Enter **winzip.zip** into the Search box at the top of the Philips web page.

- 3. Click on Microcontrollers Software support.

- 4. Download disk1.zip and disk2.zip.

- 5. Create a directory on your hard drive named WINISP.

- 6. Unzip the two disk files into this new directory WINISP.

#### Using In-System Programming (ISP)

When ISP mode is entered, the default loader first disables the watchdog timer to prevent a watchdog reset from occurring during programming.

The ISP feature allows for a wide range of baud rates to be used in the application, independent of the oscillator frequency. It is also adaptable to a wide range of oscillator frequencies. This is accomplished by measuring the bit-time of a single bit in a received character. This information is then used to program the baud rate in terms of timer counts based on the oscillator frequency. The ISP feature requires that an initial character (a lowercase f) be sent to the XA-G49 to establish the baud rate. The ISP firmware provides auto-echo of received characters.

Once baud rate initialization has been performed, the ISP firmware will only accept specific Intel Hex-type records. Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below:

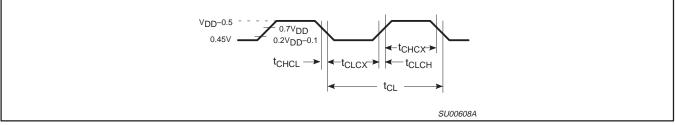

#### :NNAAAARRDD..DDCC<crlf>